Équipe ADAC

ADAptive Computing

L’équipe ADAC réunit des chercheurs et enseignants-chercheurs aux compétences complémentaires réunis autour de la thématique fédératrice de la conception de systèmes adaptatifs, composants capables de s’autogérer pour optimiser leurs performances au sens de propriétés diverses (puissance de calcul, consommation, fiabilité, sécurité). Les domaines d’application adressés sont larges, et concernent plus spécifiquement les systèmes embarqués, l’internet des objets (IoT) et les grilles de calcul. L’équipe bénéficie d’une reconnaissance nationale et internationale de ses activités, que ce soit pour les travaux menés sur les structures innovantes à base de mémoires magnétiques ou bien les travaux sur les systèmes multiprocesseurs adaptatifs.

Permanents

Abdoulaye Gamatié, Directeur de recherche, CNRS

Florent Bruguier, Maître de conférences, UM

Gilles Sassatelli, Directeur de recherche, CNRS

Lionel Torres, Professeur des universités, UM

Pascal Benoit, Maître de conférences, UM

David Novo, Chargé de recherche, CNRS

Doctorants

Rafael Carrera Rodriguez, UM

Justin Chikhaoui, CNRS

Nassim Riadi, CNRS

Ismael Samaye, UM

Soraya Mobaraki, CNRS

Aymen Romdhane, CEA

Bruno Lovison Franco, UM

Paul Delestrac, UM

Luis Bertran Alvarez, Bull SAS

Mohamed Watfa, UM

Autres personnels

Ana Tacuri, CDD Ingénieur-Technicien, CNRS

Les recherches menées par l’équipe s’inscrivent dans un des trois axes suivants, chaque permanent étant en général impliqué sur 2 axes (un axe principal et un axe secondaire).

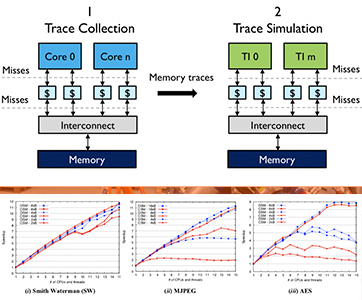

Axe 1 : Architecture matérielles et logicielles innovantes

Les recherches menées dans cet axe visent à apporter des réponses à des problèmes divers tels que l’efficacité énergétique ou l’optimisation des performances. Les approches proposées relèvent de la définition d’architectures matérielles et logicielles avec une emphase particulière portée sur l’adaptation [A1] [A2]. Les solutions sont de type systèmes multicoeurs/multiprocesseurs homogènes ou hétérogènes, l’accent étant mis sur les questions du support permettant la mise en place de solutions adaptatives[A3] (monitoring, migration d’objets logiciels) ainsi que la prise de décision (modélisation, prédiction et prise de décision). Les travaux concernent à la fois les systèmes sur puce et les grilles de calcul, avec notamment un projet innovant associant le concept de l’adaptation à un transfert d’énergie entre noeuds de calcul.

Axe 2 : Intégration technologique

Les travaux menés dans cet axe relèvent de la prise en compte ou de l’exploitation intelligente du substrat technologique pour optimiser les performances des systèmes au sens large du terme. Ceci concerne des travaux sur les technologies mémoires émergentes (MRAM notamment) avec des contributions sur des cellules hybrides, s’appuyant sur la technologie CMOS et sur des mémoires MRAM non-volatiles [I3], innovantes et brevetées, à des fins d’intégrations architecturales pour les systèmes embarqués ou encore pour la hiérarchie mémoire de systèmes multicoeurs [I1] [I2].

Des travaux sont également menés sur les réseaux de communication intégrés (NoC) avec prise en compte des procédés de fabrication (3D TSV, asynchrones, FDSOI) ou bien encore sur la construction de modèles compacts pour l’estimation de la consommation ou de la température de fonctionnement en utilisant des approches de fouille de données.

Axe 3 : Sécurité des systèmes

Enfin, l’équipe conduit des recherches dans le domaine de la sécurisation des systèmes embarqués contre différents types de menaces tels que les attaques par canaux cachés, la contrefaçon, la protection des échanges de données sur puce [S1][S2], ou encore la sécurisation des réseaux industriels et des objets connectés. Différents types de solutions ont été proposés par l’équipe qui par ailleurs gère la plateforme de sécurité numérique SECNUM (plateforme ouverte unique en France permettant l’analyse sécuritaire de circuits intégrés). Cette plateforme est utilisée à des fins de recherche mais aussi pour de la pré-évaluation de circuits industriels et pour la formation dans le cadre des Services Nationaux du GIP-CNFM.

Au-delà des recherches menées au sein de ces 3 axes, il convient de souligner que l’équipe porte une attention particulière à sa politique de prospective scientifique et dédie une partie de ses activités à des actions exploratoires.

ANR ADEQUATE-DL

Approximating Deep Learning Accelerators

PRC

ANR – AAPG2018 – CE23 Données, Connaissances, Big data, Contenus multimédias, Intelligence Artificielle

Sécurité au niveau des micro-architectures

Non Volatile MRAM-based Asynchronous PROCessor

Repenser la simulation d’architecture des ordinateurs accélérée sur FPGA pour l’exploration de stockage des données

Heterogeneous memory systems with emerging non-volatile technologies

Architecture distribuée de passerelles réseaux interopérables et collaborative

Le rayonnement des membres de l’équipe se caractérise à partir des indicateurs suivants sur la période 2013-2016 :

Evaluation / Expertise

Comité d’Evaluation ANR Défis Micro et Nanotechnologies,

Membre du comité Scientifique de l’ANR Nanosciences & STIC,

Participations à plusieurs groupes de travail prospectifs,

Croucher Fundation – Fondation privée pour la recherche – Hong-Kong

Communication et événements scientifiques

Organisation du Colloque BRAFITEC 2016 (Franco-Brésilien)

Création du workshop RECOSOC, organisation des éditions 2011 et 2014

Membre de Comités de pilotage : IEEE FPL, RECOSOC, IEEE ISVLSI, CRYPTARCHI, IEEE NVMSA,

Working group IFIP 10.5 : « Design and Engineering of Electronic Systems »,

Associate Editor : ACM Transactions on Embedded Computing Systems,

Membre de comité des programmes des principales conférences du domaine.

- IMEC, Interuniversity Microelectronics Centre, Belgium

- Brême University, Germany

- ETH Zurich, Swiss Federal Institute of Technology in Zurich, Suisse

- NAU, Northern Arizona University, USAYale University, USA

- Universidade Federal de Minas Gerais et Universidade Federal da Bahia, Brésil

- Université de Pittsburg, USA

- Université d’Oran, Algérie

- Université d’Aalborg, Danemark

We are always looking for highly qualified and motivated students and researchers. Feel free to apply.